Embedded FPGA Developments in 130nm and 28nm CMOS for Machine Learning in Particle Detector Readout

Published in In submission to JINST, 2024

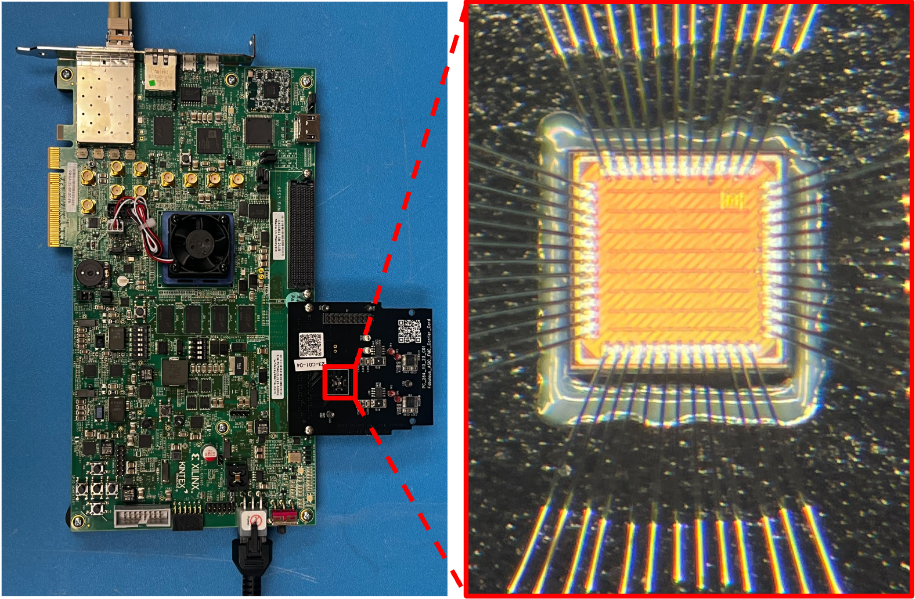

Embedded field programmable gate array (eFPGA) technology allows the implementation of reconfigurable logic within the design of an application-specific integrated circuit (ASIC). This approach offers the low power and efficiency of an ASIC along with the ease of FPGA configuration, particularly beneficial for the use case of machine learning in the data pipeline of next-generation collider experiments. An open-source framework called ‘FABulous’ was used to design eFPGAs using 130 nm and 28 nm CMOS technology nodes, which were subsequently fabricated and verified through testing. The capability of an eFPGA to act as a front-end readout chip was assessed using simulation of high energy particles passing through a silicon pixel sensor. A machine learning-based classifier, designed for reduction of sensor data at the source, was synthesized and configured onto the eFPGA. A successful proof-of-concept was demonstrated through reproduction of the expected algorithm result on the eFPGA with perfect accuracy. Further development of the eFPGA technology and its application to collider detector readout is discussed.

Recommended citation: J. Gonski et al., (2023). "Embedded FPGA Developments in 130nm and 28nm CMOS for Machine Learning in Particle Detector Readout." in submission to JINST. https://arxiv.org/abs/2404.17701